ZL30795LFG7

Synchronous Ethernet Packet Clock Network Synchronizers

Inventory:8,656

- 90-day after-sales guarantee

- 365 Days Quality Guarantee

- Genuine Product Guarantee

- 7*24 hours service quarantee

-

Part Number : ZL30795LFG7

-

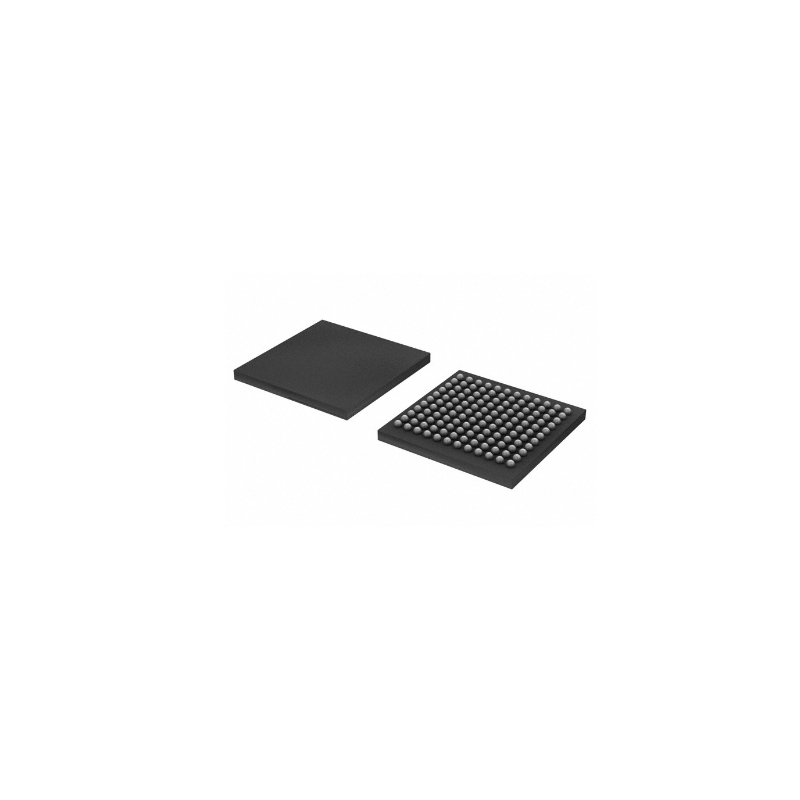

Package/Case : VFLGA-80

-

Brands : MICROCHIP

-

Components Categories : Clock Generators & Support Products

-

Datesheet : ZL30795LFG7 DataSheet (PDF)

Overview of ZL30795LFG7

The ZL30795 offers two independent timing channels of a combined hardware and software platform including IEEE 1588-2008 Precision Time Protocol Stack and Synchronization Algorithms. Using Microsemi’s miTimePLL timing technology, this device offers new and improved features for 5G transport and wireless infrastructure equipment. This devices is ideal for timing card applications in systems that need to support 10G/40G and 100G Phys.

Click here for the list of supported IEEE 1588-2008 PTP Profiles and Equipment Clock Specifications

Under the same family, the ZL3066x and ZL3069x offer one to three channels of Synchronous Ethernet (SyncE) packet clock synchronization for line card and timing card interface.

Log in to your MyMicrochip account (with SDE enabled) and request for data sheet and the following application notes.

AN3467 Crystals and Oscillators for Next Generation Timing Solutions

ZLAN-649 ZL3067x Power Supply Decoupling and Layout Practices

ZLAN-656 Redwood PSNR

ZLAN-664 Board Design Recommendations for Redwood

ZLAN-672 Generating JESD204B Clock SYSREF Using Redwood

ZLAN-683 Assembly and PCB Layout Guidelines for 80-lead LGA Package

ZLAN-724 Phase Measurement Compensation for Redwood

ZLAN-728 Indirect Read and Write Procedure

Key Features

- Applications/Uses

- Central timing function for carrier network equipment compliant to ITU-T G.8262, G.8273.2, G.8273.4

- Communications systems timed by any combination of Synchronous Ethernet, IEEE 1588 PTP, or GPS/GNSS

- 5G wireless CU, DU, and RU systems

- 5G systems with precise time requirements driven by advanced services such as carrier aggregation, coordinated multipoint, OTDOA location, etc.

- Integrated basestation reference clock for 2G through 5G macro and micro cells

- Carrier routers, access aggregation, wireless backhaul

- SONET/SDH systems

Specifications

The followings are basic parameters of the part selected concerning the characteristics of the part and categories it belongs to.

| Manufacturer | Microchip | Product Category | Clock Generators & Support Products |

| RoHS | Details | Package / Case | VFLGA-80 |

| Brand | Microchip Technology | Product Type | Clock Generators |

| Factory Pack Quantity | 176 | Subcategory | Clock & Timer ICs |

Warranty & Returns

Warranty, Returns, and Additional Information

-

QA & Return Policy

Parts Quality Guarantee: 365 days

Returns for refund: within 90 days

Returns for Exchange: within 90 days

-

Shipping and Package

Shipping:For example, FedEx, SF, UPS, or DHL.UPS, or DHL.

Parts Packaging Guarantee: Featuring 100% ESD anti-static protection, our packaging incorporates high toughness and superior buffering capabilities.

-

Payment

For example, channels like VISA, MasterCard, UnionPay, Western Union, PayPal, and more.

If you have specific payment channel preferences or requirements, please get in touch with our sales team for assistance.

Similar Product

ZL30363GDG2

Clock Generator 0.0000001MHz to 750MHz-IN 750MHz-OUT 144-Pin LBGA Tray

ZL38063LDF1

Audio DSPs Audio Processor for Security Camera and ASR Assist

KSZ8895MQXIA

High-speed networking switch

MIC2951-02YM

High Performance Power Supply Controller

LAN91C111I-NU

Ethernet controller

DSPIC30F4011-30I/PT

This device is ideal for applications requiring fast processing capabilities and efficient memory management

PIC16F722-I/SP

Simulated Roller

PIC12F508-I/P

The PIC12F508-I/P is a microcontroller from the PIC12 family, specifically the PIC12F5xx series, with 8-bit architecture